Architecture

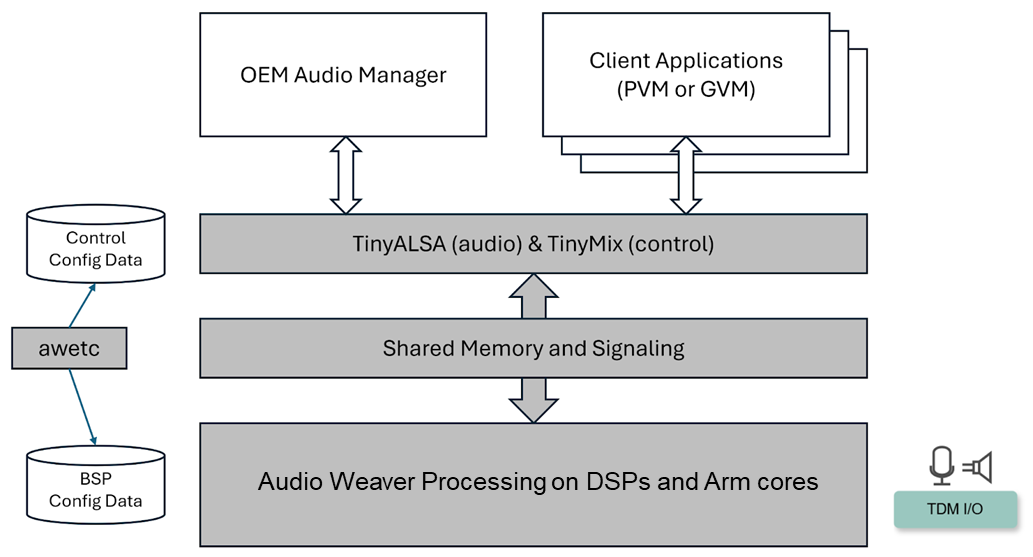

The high-level architecture is shown below. All of the client interactions with Audio Weaver are through TinyALSA (for real-time audio) and TinyMix (for control) plugins. Internally, Audio Weaver communicates with the plugins through shared memory and IPCC signaling. Additionally, there are configuration files generated through the Audio Weaver Target Configurator (awetc) application. One of the configuration files (awe_config.bin) is used to configure the audio processing cores and contains information such as heap sizes and number of threads. There is a second configuration file (awc_index.txt) containing information about tunable variables and ALSA devices.

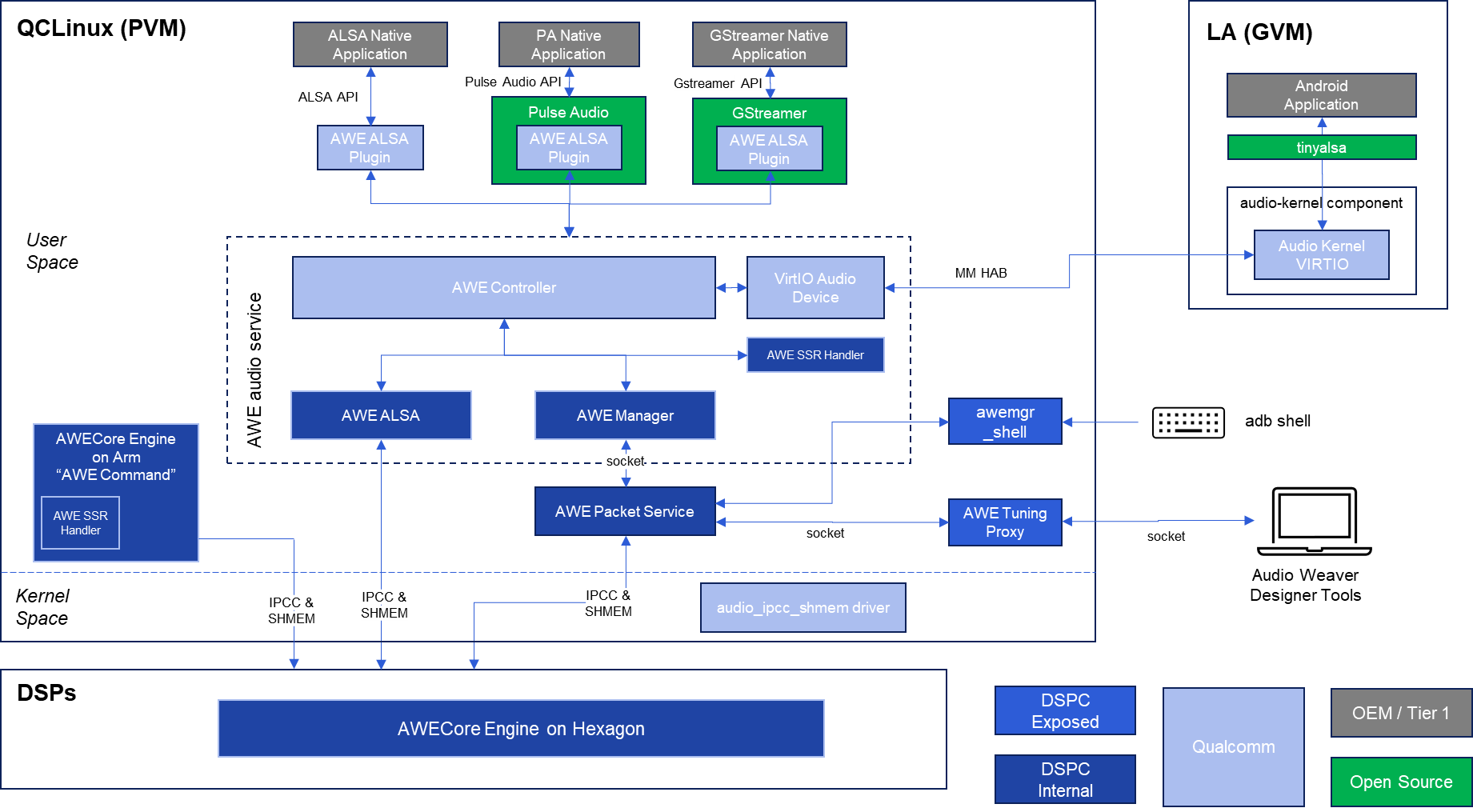

A more detailed view is shown below. This is to help you understand the inner workings but in reality there are only a few exposed and documented interface points for OEMs and Tier 1’s:

-

Audio APIs like ALSA, Pulse Audio, and GStreamer

-

TinyAlsa and TinyMix

-

awemgr_shell for command line control of the audio processing during development

-

AWE Tuning Proxy for connecting the Audio Weaver Designer tools

Audio I/O

Audio I/O is configured using modules in the Audio Weaver signal flow. There are currently modules for:

-

TDM serial port I/O

-

ALSA audio from the HLOS

In the future, this will be extended to include

-

USB audio I/O

-

Ethernet AVB

Audio Processors

The integration includes access to all audio processing cores in the SOC. For the Gen 4 SOC SA8255, this includes:

-

0- ADSP

-

1- GPDSP0

-

2- GPDSP1

-

3- Arm

Each of these DSPs is a single core Hexagon (ADSP has 4 threads; GPDSPs have 6 threads). For the Gen 5 SA8397 / SA8797 SOC, this includes:

-

0- DSP0

-

1- DSP1

-

2- DSP2

-

3- Arm

Each Gen 5 DSP has dual Hexagon cores with 12 threads. Qualcomm will offer performance levels of the Gen 5 silicon which expose 1, 2, or 3 DSPs. Only the highest performance tier has 3 dual core DSPs.

In all cases, the Arm library is able to extend processing across Arm cores using the scheduling capabilities of the operating system. Thus, only a single instance of the Audio Weaver Arm library is needed and it is able to leverage all of the Arm cores. The cores will be ordered as shown above in the BSP code. (Putting the Arm at the end provides consistency between the Gen4 and Gen5 processor families.)

Clock Configuration

The system configuration file contains the default processor speed settings for the audio processors. When the system boots, the Hexagon DSPs are set to the speed listed in the configuration file. The Arm processor speed is not changed.

The SnapdragonClockVoting module can be used to adjust the processor speed and DDR memory speed of the Hexagon DSPs at run-time. Here are the default clock speeds provided in the release:

SA8255

| Processor | Default Speed | Max Speed |

|---|---|---|

| ADSP | 1.344 GHz | 1.344 GHz |

| GPDSP0 | 1.708 GHz | 1.708 GHz |

| GPDSP1 | 1.708 GHz | 1.708 GHz |

| Arm | 2.1 GHz | 2.1 GHz. |

SA8797

| DSP0 | 1.574 GHz |

|---|---|

| DSP1 | 1.574 GHz |

| DSP2 | 1.574 GHz |

| Arm | 2.1 GHz |

Audio Processor Local Memory

Audio Weaver defines 4 memory heaps that are available to the audio modules. The first 3 heaps are private to each audio processing core

-

Fast

-

FastB

-

Slow

The 4th heap enables communication and synchronization between cores:

- Shared

The sizes of these heaps are defined in the startup XML initialization file and can be increased / decreased by the user without recompilation. The first 3 heaps (Fast, FastB, and Slow) are allocated from DDR. The Shared heap comes from carved out DDR memory. Memory for the Arm instance is dynamically allocated using malloc(). The tables below summarize the default heap sizes in the base distributions:

SA8255

| Processor | Fast | Fast B | Slow | Shared |

|---|---|---|---|---|

| ADSP | 250 kword | 250 kword | 250 kword | 262 kword |

| GPDSP0 | 250 kword | 250 kword | 250 kword | 262 kword |

| GPDSP1 | 250 kword | 250 kword | 250 kword | 262 kword |

| Arm | 4 Mword | 2 Mword | 1 Mword | 262 kword |

SA8397 / SA8797

| Processor | Fast | Fast B | Slow | Shared |

|---|---|---|---|---|

| DSP0 | 0.5 MB (TCM) | 1 MB (DDR) | 1 MB (DDR) | TBD |

| DSP1 | 0.5 MB (TCM) | 1 MB (DDR) | 1 MB (DDR) | TBD |

| DSP2 | 0.5 MB (TCM) | 1 MB (DDR) | 1 MB (DDR) | TBD |

| Arm | 4 MB (DDR) | 4 MB (DDR) | 4 MB (DDR) | TBD |